Peripheral Component Interconnect

PCI (ang. Peripheral Component Interconnect) – magistrala komunikacyjna służąca do przyłączania kart rozszerzeń do płyty głównej w komputerach klasy PC.

Po raz pierwszy została publicznie zaprezentowana w czerwcu 1992 r. jako rozwiązanie umożliwiające szybszą komunikację pomiędzy procesorem i kartami niż stosowane dawniej ISA. Dodatkową zaletą PCI jest to, że nie ma znaczenia czy w gnieździe jest karta sterownika dysków (np. SCSI), sieciowa czy graficzna. Każda karta, pasująca do gniazda PCI, funkcjonuje bez jakichkolwiek problemów, gdyż nie tylko sygnały, ale i przeznaczenie poszczególnych styków gniazda są znormalizowane.

W przeciwieństwie do innych magistrali, przykładowo VESA Local Bus, która początkowo była stosowana tylko do przyspieszenia operacji graficznych, szyna PCI stanowi kompleksowe rozwiązanie, przyspieszające współpracę z dowolnym urządzeniem zewnętrznym. Przy częstotliwości taktowania 33 MHz i szerokości 32 bitów magistrala PCI osiąga szybkość transmisji 132 MB/s. Szerokość szyny adresowej i danych wprowadzonych procesorów 64-bitowych nie wpływa na architekturę PCI, a jedynie podwaja jej przepustowość do 264 MB/s.

Karty dołączone do szyny PCI mogą się komunikować nawet bez udziału mikroprocesora, dzięki czemu wzrasta jego rzeczywista wydajność. Dla każdej karty zdefiniowane są tzw. rejestry konfiguracyjne; przy ładowaniu systemu procesor odczytuje zapisane w nich dane i rozpoznaje, jaka karta jest umieszczona w gnieździe. Instalacja i inicjacja takiej karty następuje potem w pełni automatycznie (zob. Plug and Play).

Aby zapewnić zarówno producentom, jak i użytkownikom możliwie dużą elastyczność, w standardzie PCI zdefiniowano tzw. gniazdo wspólne (ang. shared slot). Jest to gniazdo, które może zostać użyte z kartami przystosowanymi do magistral ISA, EISA czy MCA. Umożliwia to także produkcję kart jednocześnie przystosowanych do PCI i tychże wymienionych magistral.

Bardzo istotną cechą architektury PCI jest jej skalowalność: w jednym komputerze może być równolegle lub szeregowo połączonych kilka magistral PCI. Nad koncepcją PCI Local Bus pracowało wielu znaczących producentów komputerów, z których każdy starał się, aby sprzęt obecnie przez niego produkowany był z tym standardem zgodny. Przykładowo, rozwiązanie jest na tyle elastyczne, że uwzględnia możliwość współpracy magistrali nie tylko z komputerami wyposażonymi w procesory firmy Intel, ale również z AMD i Cyrix, a także w opartych na procesorze PowerPC komputerach Pegasos. 32-bitowy standard adresowania PCI został użyty również w innych magistralach (np. AGP).

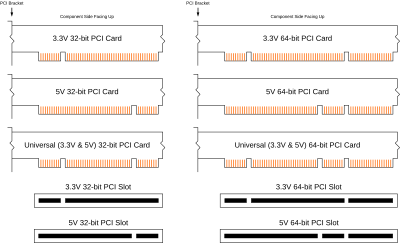

Kolejną istotną cechą PCI jest wysoka zgodność pomiędzy poszczególnymi wersjami PCI, jak i rozwiązań pochodnych (np. PCI-X) przejawiająca się tym, że urządzenia mogą pracować zarówno w starszych jak i nowszych typach gniazd, pod warunkiem że są dopasowane napięciowo (warianty 3,3 V i popularniejszy 5 V). Zgodność ta nie jest jednak zachowana w stosunku do PCI Express, która aktualnie wyparła PCI oraz AGP.

Wersje PCI Wersja PCI 2.0 PCI 2.1 PCI 2.2 PCI 2.3 Rok wprowadzenia 1993 1994 1999 2002 Maksymalna szerokość szyny danych 32 bity 64 bity 32 bity 64 bity Maksymalna częstotliwość taktowania[1] 33 MHz 33 MHz 66 MHz 66 MHz Maksymalna przepustowość[1] 132 MB/s 264 MB/s 264 MB/s 532 MB/s Napięcie 5 V 5 V 5 V / 3,3 V 3,3 V

Styki

edytujZłącze PCI określa się jako slot bądź złącze krawędziowe (ang. edge connector) posiadające 62 styki z każdej strony, ale dwa bądź cztery z nich są zastąpione przez klucz wycięcia, tak więc karta posiada 60 bądź 58 styków po każdej stronie. Pierwszy styk jest umiejscowiony najbliżej tylnej ścianki obudowy. Strony B oraz A są umieszczone kolejno, patrząc w kierunku dołu na złącze płyty głównej[1][2][3].

Opis styków 32-bitowego złącza PCI Styk Strona B Strona A Opis 1 –12 V TRST# Styki portu JTAG (opcjonalne) 2 TCK +12 V 3 Masa TMS 4 TDO TDI 5 +5 V +5 V 6 +5 V INTA# Linie przerwań 7 INTB# INTC# 8 INTD# +5 V 9 PRSNT1# Zarezerwowany Odłączone aż do momentu uzyskania wymaganej mocy 7,5 W albo 25 W 10 Zarezerwowane IOPWR +5 V albo +3,3 V 11 PRSNT2# Zarezerwowany Odłączone aż do momentu uzyskania wymaganej mocy 7,5 W albo 25 W 12 Masa Masa Klucz wycięcia dla kart obsługujących napięcie 3,3 V 13 Masa Masa 14 Zarezerwowany 3,3 V aux Zasilanie w trybie gotowości (opcjonalne) 15 Masa RST# Zresetowanie szyny 16 CLK IOPWR 33/66 MHz clock 17 Masa GNT# Szyna danych otrzymana od płyty głównej dla karty 18 REQ# Masa Szyna danych wymagana przez kartę dla płyty głównej 19 IOPWR PME# Power management event – możliwość zarządzania zasilaniem (włączenie/wyłączenie komputera) (opcjonalne) 20 AD[31] AD[30] Szyna adresowa/szyna danych (górna połowa) 21 AD[29] +3,3 V 22 Masa AD[28] 23 AD[27] AD[26] 24 AD[25] Masa 25 +3,3 V AD[24] 26 C/BE[3]# IDSEL 27 AD[23] +3,3 V 28 Masa AD[22] 29 AD[21] AD[20] 30 AD[19] Masa 31 +3,3 V AD[18] 32 AD[17] AD[16] 33 C/BE[2]# +3,3 V 34 Masa FRAME# Szyna danych jest w trakcie transferu 35 IRDY# Masa Inicjator gotowy 36 +3,3 V TRDY# Cel gotowy 37 DEVSEL# Masa Cel wybrany 38 Masa STOP# Cel wymaga wstrzymania 39 LOCK# +3,3 V Zamknięcie transakcji 40 PERR# SMBCLK SDONE Błąd parzystości; SMBus clock 41 +3,3 V SMBDAT SBO# Dane SMB 42 SERR# Masa Błąd systemu 43 +3,3 V PAR 44 C/BE[1]# AD[15] Szyna adresowa/szyna danych (dolna połowa) 45 AD[14] +3,3 V 46 Masa AD[13] 47 AD[12] AD[11] 48 AD[10] Masa 49 M66EN Masa AD[09] 50 Masa Masa Klucz wycięcia dla kart obsługujących napięcie 5 V 51 Masa Masa 52 AD[08] C/BE[0]# Szyna adresowa/szyna danych (dolna połowa) 53 AD[07] +3,3 V 54 +3,3 V AD[06] 55 AD[05] AD[04] 56 AD[03] Masa 57 Masa AD[02] 58 AD[01] AD[00] 59 IOPWR IOPWR 60 ACK64# REQ64# 64-bitowe rozszerzenie; nie podłączać do 32-bitowych urządzeń 61 +5 V +5 V 62 +5 V +5 V

64-bitowy PCI jest rozszerzony o dodatkowe 32 kontakty po każdej stronie, które zapewniają AD[63:32], C/BE[7:4]#, PAR64 sygnał parzystości oraz liczba styków zasilania i masy.

Legenda Styk masy Odniesienie do napięcia 0 V Styk zasilania Dostarcza zasilanie dla karty PCI Styk wychodzący Sygnał sterowany przez kartę PCI, otrzymywany przez płytę główną Wyjście inicjatora Sygnał sterowany przez układ nadrzędny/inicjatora, otrzymywany przez cel Sygnał wejścia/wyjścia Może być sterowany przez inicjatora bądź cel, zależnie od operacji Wyjście celu Sygnał sterowany przez cel, otrzymywany przez inicjatora/układ nadrzędny Wejście Sygnał sterowany przez płytę główną, otrzymywany przez kartę PCI Otwarty dren Może zostać odłączony i/lub odczytany przez wiele kart Zarezerwowany Obecnie nie stosowany, nie podłączać

Większość linii magistrali połączona jest do każdego slotu równolegle. Wyjątkami są:

- Każdy slot posiada swoje własne wyjście REQ# oraz wejście GNT# z arbitra płyty głównej.

- Każdy slot posiada swoją własną linię IDSEL, przeważnie podłączoną do określonej linii AD.

- TDO jest połączone łańcuchowo do kolejnych slotów TDI. Karty bez wsparcia JTAG muszą podłączyć TDI do TDO, tak aby nie przerwać łańcucha.

- PRSNT1# i PRSNT2# posiadają własne odłączane rezystory na płycie głównej. Płyta główna może (ale nie musi) wykryć te styki w celu ustalenia poboru mocy na obecnych kartach PCI.

- REQ64# i ACK64# są indywidualnie odłączane na slotach 32-bitowych.

- Linie przerwań (INTA#, INTB#, INTC# oraz INTD#) są podłączone do każdego ze slotów w innej kolejności (INTA# na jednym slocie to INTB# na następnym, a INTC# na kolejnym).

Dodatkowe informacje:

- IOPWR podaje +3,3 V albo +5 V w zależności od konstrukcji płyty głównej. Sloty posiadają również klucze w odpowiednich miejscach, co zapobiega podłączeniu nieodpowiedniej karty rozszerzeń.

Przypisy

edytuj- ↑ a b c PCI Local Bus Specification, revision 2.3. PCI Special Interest Group, 2002-03-29. [dostęp 2009-07-07].

- ↑ PCI Local Bus Specification, revision 3.0. PCI Special Interest Group, 2002-08-12. [dostęp 2009-07-07].

- ↑ PCI Connector Pinout.